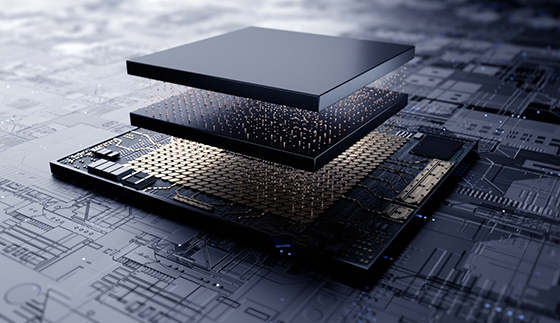

삼성전자, 7나노 EUV 시스템반도체에 3차원 적층 기술 업계최초 적용

복수의 칩을 적층해 하나의 반도체로 만드는 3D 적층 기술 ‘X-Cube’

(서울=NSP통신) 이복현 기자 = 삼성전자가 업계최초로 7나노 EUV 시스템반도체에 3차원 적층 패키지 기술인 X-Cube(eXtended-Cube)를 적용한 테스트칩 생산에 성공했다.

이로써 삼성전자는 최첨단 EUV 초미세 전공정뿐 아니라 후공정에서도 첨단 기술 경쟁력을 확보하게 됐으며, 이는 반도체 비전 2030을 달성하는데 큰 역할을 할 것으로 기대된다.

X-Cube는 전공정을 마친 웨이퍼 상태의 복수의 칩을 위로 얇게 적층해 하나의 반도체로 만드는 기술이다.

시스템반도체는 일반적으로 CPU·GPU·NPU 등의 역할을 하는 로직 부분과 캐시메모리(Cache memory) 역할을 하는 SRAM 부분을 하나의 칩에 평면으로 나란히 배치해 설계한다.

X-cube 기술은 로직과 SRAM(Static Random Access Memory)을 단독으로 설계·생산해 위로 적층하기 때문에 전체 칩 면적을 줄이면서 고용량 메모리 솔루션을 장착할 수 있어 고객의 설계 자유도를 높일 수 있다.

또 실리콘관통전극(TSV) 기술을 통해 시스템반도체의 데이터 처리속도를 획기적으로 향상 시킬 수 있고, 전력 효율도 높일 수 있다.

이외 위아래 칩의 데이터 통신 채널을 고객 설계에 따라 자유자재로 확장할 수 있고, 신호 전송 경로 또한 최소화할 수 있어 데이터 처리 속도 극대화할 수 있다는 장점이 있다.

이 기술은 슈퍼컴퓨터·인공지능·5G 등 고성능 시스템반도체를 요구하는 분야는 물론 스마트폰과 웨어러블 기기의 경쟁력을 높일 수 있는 핵심 기술로 활용될 것으로 예상된다.

글로벌 팹리스 고객은 삼성전자가 제공하는 X-Cube 설계방법론(Design Methodology)과 설계툴(Design Flow)을 활용해 EUV 기술 기반 5, 7나노 공정 칩 개발을 바로 시작할 수 있다.

특히 이미 검증된 바 있는 삼성전자의 양산 인프라를 이용할 수 있기 때문에 개발 오류를 빠르게 확인하며 칩 개발 기간을 줄일 수 있다.

삼성전자 파운드리사업부 마켓전략팀 강문수 전무는 “EUV 장비가 적용된 첨단 공정에서도 TSV 기술을 안정적으로 구현해냈다”며 “삼성전자는 반도체 성능 한계 극복을 위한 기술을 지속 혁신해 나가겠다”고 밝혔다.

한편 삼성전자는 8월 16일부터 18일까지 온라인으로 진행되는 HPC·AI 등의 고성능 반도체 관련 연례 학술 행사인 핫 칩스(Hot Chips) 2020에서 X-Cube의 기술 성과를 공개할 계획이다.

NSP통신 이복현 기자 bhlee2016@nspna.com

저작권자ⓒ 한국의 경제뉴스통신사 NSP통신·NSP TV. 무단전재-재배포 금지.

![[NSPAD]삼성전자](https://file.nspna.com/ad/T01_samsung_5043.gif)

![[NSP7컷]인터넷은행의 혁신적인 배신 [NSP7컷]인터넷은행의 혁신적인 배신](https://file.nspna.com/news/2023/05/30/photo_20230530123951_639759_0.jpg)

![[NSP PHOTO][재계·산업 업계동향]한화오션·SK이노베이션 조선·LNG 확대…AI·조직문화 혁신 병행](https://file.nspna.com/news/2026/02/19/20260219165815_803395_0.png)

![[NSP PHOTO][제약·바이오업계동향]셀트리온, 임상데이터 공개·유한양행, 다국가 시험 착수…신약개발 속도](https://file.nspna.com/news/2026/02/19/20260219163524_803390_0.png)

![[NSP PHOTO][업앤다운]제약주 상승…부광약품↑· 모아라이프플러스↓](https://file.nspna.com/news/2026/02/19/20260219161110_803377_0.png)

![[NSP PHOTO][들어보니]유한양행, 알레르기 질환 치료제 임상2상 착수…유효·안전성 객관적 평가 예정](https://file.nspna.com/news/2026/02/19/20260219152942_803352_0.jpg)

![[NSP PHOTO][들어보니]코스닥 대규모 퇴출 예고…시장 건전성 강화 vs 고의 상폐 악용 우려](https://file.nspna.com/news/2026/02/12/20260212160718_802826_0.png)

![[NSP PHOTO][들어보니]KT 6G 경쟁력, 속도에 AI 더해진다…표준 선점 경쟁 본격화](https://file.nspna.com/news/2026/02/11/20260211171637_802579_0.jpg)

![종근당[N06] [NSPAD]종근당](https://file.nspna.com/ad/N06_jonggdang_5089.jpg)

![하나금융그룹[N06] [NSPAD]하나금융그룹](https://file.nspna.com/ad/N06_hanagroup_5083.jpg)

![[NSP PHOTO][금융업계기상도]IBK기업은행 비온뒤갬·NH농협은행 구름조금](https://file.nspna.com/news/2026/02/13/20260213165914_803173_0.jpg)

![[NSP PHOTO][그룹주 기상도]삼성·HD현대 쾌청…경영권·주주 갈등 겪는 LG·태광 흐림](https://file.nspna.com/news/2026/02/13/20260213165904_803172_0.png)

![[NSP PHOTO][증권업계기상도]신한투자증권 맑음, 20·30세대 겨냥한 발행어음 특판 출시·대신증권 맑음, 자사주 1535만주 소각](https://file.nspna.com/news/2026/02/13/20260213163357_803158_0.png)

![[NSP PHOTO]코스닥, 상폐 개혁 본격화…부실기업 퇴출 속도전](https://file.nspna.com/news/2026/02/19/photo_20260219135336_803308_0.png)

![[NSP PHOTO]신한투자증권, 조각투자 발행·유통 협력 체결…디지털 자산 생태계 구축 본격화](https://file.nspna.com/news/2026/02/19/photo_20260219105935_803283_0.jpg)

![[NSP PHOTO]두산로지스틱스솔루션, 아성다이소 양주허브센터 수주…1620억원 규모 옴니채널 물류 거점 구축](https://file.nspna.com/news/2026/02/19/photo_20260219103649_803278_0.jpg)

![[NSP PHOTO]최윤범 고려아연 회장, IEA 각료이사회 핵심광물 공급망 세션 의장 수행…국제협력 필요성 강조](https://file.nspna.com/news/2026/02/19/photo_20260219153540_803357_0.jpg)

![[NSP PHOTO]박세진 세일즈포스 코리아 대표 신약개발부터 시장 진출까지 데이터 하나로…제약·헬스케어 등 규제산업 진출 가속화 나서](https://file.nspna.com/news/2026/02/13/photo_20260213154214_802995_0.jpg)

![[NSP PHOTO]남자 간호사 합격자 10년 새 4배 증가…누적 4만명 돌파](https://file.nspna.com/news/2026/02/13/photo_20260213144434_803116_0.jpg)

![[NSP PHOTO]포스코차세대 함정, 소재가 생존성 결정…스펙 업으로 표준 주도](https://file.nspna.com/news/2026/02/12/photo_20260212172714_802860_0.jpg)

![[NSP PHOTO]한화오션, 캐나다 조선소·대학과 협력…기술이전·해군사업 기반 구축](https://file.nspna.com/news/2026/02/19/photo_20260219163939_803391_0.jpg)

![[NSP PHOTO]그라비티, 25년 매출 전년比 11.8%↑…영업이익 770억](https://file.nspna.com/news/2026/02/19/photo_20260219153747_803359_0.jpg)

![[NSP PHOTO]유한양행, 알레르기 질환 치료제 임상2상 착수…유효·안전성 객관적 평가 예정](https://file.nspna.com/news/2026/02/19/photo_20260219152942_803352_0.jpg)

![[NSP PHOTO][타보니]KGM 액티언 하이브리드, 성능·가성비 좋은 도심형 SUV](https://file.nspna.com/news/2025/12/17/20251217164713_793348_0.jpg)

![[NSP PHOTO][타보니]KGM 무쏘 EV, 세단 같은 정숙성·효율 좋은 전비에 잘 팔리는 픽업트럭](https://file.nspna.com/news/2025/12/04/20251204123011_790796_0.jpg)

![[NSP PHOTO][타보니]캐딜락 전기차 에스컬레이드IQ, 슈퍼크루즈 탑재 4.2톤 불구 연비 준수](https://file.nspna.com/news/2025/12/02/20251202154914_790331_0.jpg)